# Address Discharge Simulation of Additional Pulse Application to Common Electrode in AC PDP

BYUNG-GWON CHO,<sup>1,\*</sup> YEON TAE JEONG,<sup>1</sup> AND HEUNG-SIK TAE<sup>2</sup>

<sup>1</sup>Department of Display Engineering, College of Engineering, Pukyong National University, Busan, Korea

<sup>2</sup>Department School of Electronics Engineering, College of IT Engineering, Kyungpook National University, Daegu, Korea

The address discharge simulation and the light waveform are investigated when the additional pulses are applied to the common electrode during an address period in AC plasma display panel. The wall charges in a cell are accumulated on three electrodes during a reset period and those are utilized to produce the address discharge triggering in addition to the externally applied voltage between the scan and address electrodes during an address period. As the accumulated wall charges should be utilized on the overall electrodes to improve the address discharge triggering, the additional pulses are applied to the common sustain electrodes when the scan and address pulses are driven. In this study, the Xe <sup>3</sup>P<sub>2</sub> energy state to generate the vacuum ultraviolet are simulated when the scan and address pulses on two electrode are applied including the additional pulses on the common electrodes. In addition, the address discharge light waveforms in the conventional and the proposed driving method are measured and compared.

Keywords Discharge simulation; Wall charge; Common electrode; AC PDP

## 1. Introduction

One of the main issues in the driving method of the AC plasma display panel is the high speed addressing technique because the percentage rate of the address period to select a displaying cell for one TV frame time is close to 50% [1]. Therefore, only about 30% time is occupied by the sustain period for production of the luminance with exception of the reset and address period. That is, the reset and address period without production of the luminance spend time about 70%. Many previous studies have been suggested to shorten the address period [2, 3]. Among them, the new driving method was reported that the pulse to improve the address discharge characteristic was applied to the common electrodes when the scan and address pulses are applied during an address period [4]. However, that paper only measured the light waveform with changes in pulse amplitude and applying time, but the experimental measurement and explanation for the change of the wall charge in a cell and the production of the plasma discharge was poor. Reviewing the previous paper,

<sup>\*</sup>Address correspondence to Byung-Gwon Cho, Department of Display Engineering, Pukyong National University, Busan, 608-737, Korea. E-mail: bgcho@pknu.ac.kr

Color versions of one or more of the figures in the article can be found online at www.tandfonline.com/gmcl.

the used driving method for the experiment is introduced simply. In the reset period of the conventional driving method, the wall charges are accumulated on three electrodes by applying the high positive-going ramp waveform and properly redistributed by applying the negative-going ramp waveform. After a reset period, the negative wall charges are accumulated on the X and Y electrodes, and the positive wall charges on the A electrode. The address triggering discharge during an address period was produced by application of the scan pulse on the Y electrode and the address pulse on the A electrode after a reset period. Due to the generation time of this address triggering discharge, the address discharge time is delayed and the address pulse width is determined by the production time of the stable address discharge. To reduce the address discharge delay time, much wall charges should be accumulated during a reset period or the applied scan and address voltages should be increased, but it reaches the limit due to various reasons [5, 6]. The address discharge delay time may be reduced if the negative charges on the X electrode could be utilized for the address triggering discharge by application of the pulses on the X electrode at the same time when the scan and address pulse applied. Namely, the address discharge characteristics will be improved if the wall charges accumulated on the overall electrodes could be utilized for the address triggering discharge. In the previous work, the address discharge time lag could be reduced approximately 200 ns under the optimum voltage height and pulse applying time conditions on the X electrode comparing with the conventional driving method without the negative-going pulse during an address period.

In this study, the intensity of the address discharge and the amount of the wall charges during an address period are analyzed when applying the conventional driving waveform using the simulation program made by previous research [7, 8]. When the proposed driving waveform is adopted to AC PDP based on the wall charge distribution after a reset period, how the address discharge occurs by using the simulation results is compared with the conventional driving waveform. In addition, comparing those simulation results with the measured address light waveforms, the changes in the wall charge distribution of a cell is confirmed and studied.

## 2. Experiment

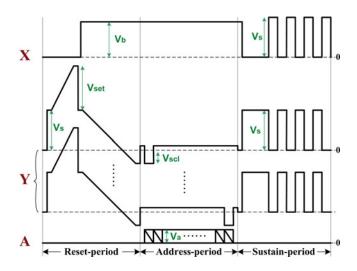

Figure 1 shows the conventional driving waveform applied to three electrodes during a reset, address, and sustain periods in one subfield time. The X waveform applied to the sustain electrode with horizontal line on the front plate, the Y waveforms applied to the scan electrodes line-by-line, and the A waveform applied to the vertical address electrode. During a reset period, the wall charge was accumulated on three electrodes and redistributed to facilitate the production of the address discharge in a cell. When a scan pulse on the Y electrode and an address pulse on the A electrode during an address period were applied, an address discharge was produced and the wall charge distribution was changed at a selected cell for displaying. In the sustain period, the square pulses alternately applied to the X and Y electrodes and the sustain discharges were continuously generated at the selected cell in an address period (Table 1).

The address discharge delay time during an address period was determined by the sum of the amount of the accumulated wall charge in a cell and the amplitude of the externally applied voltage, the scan and address pulses. If the distribution of the wall charge accumulated by the reset waveform could be assumed, a way to efficiently use the wall charges could be found to improve address discharge. It is generally known that the negative charges were accumulated on the X and Y electrodes, while the positive charges on the

Figure 1. Conventional driving waveform including reset, address, and sustain period during one subfield time.

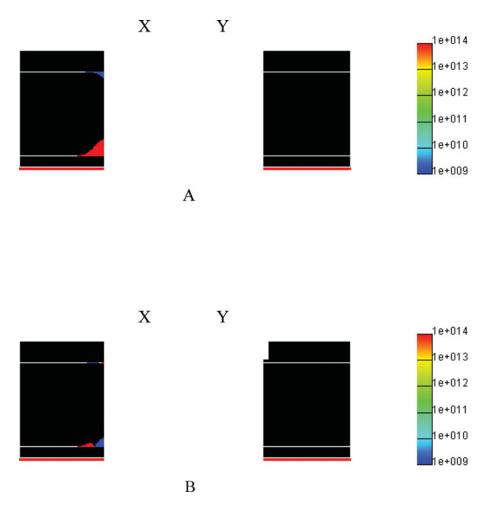

A electrode after a reset period in a cell [9]. Figure 2 shows the wall charge distribution expressed by the simulation result before (a) and after (b) address discharge. The area of the blue and red colors meant the negative and the positive wall charge distribution, respectively.

Looking at the simulation result for the wall charge distribution, it was found that the negative charges were accumulated on the X and Y electrodes and the positive charges were on the A electrode before addressing, after a reset period, as shown in Figure 2(a). However, in Figure 2(b), the positive charge were accumulated on the Y electrode and the negative charge were on the A electrode after address discharge between the Y and A electrodes by applying the scan and address pulses. Meanwhile, comparing Figure 2(a) to 2(b), it was found the amount of the wall charge on the X electrode did not change. In this sense, if the wall charge on the X electrode could be utilize at a production time of the address discharge during an address period, it is expect that the address discharge is produced fast and the discharge intensity is also increased.

#### 3. Result and Discussion

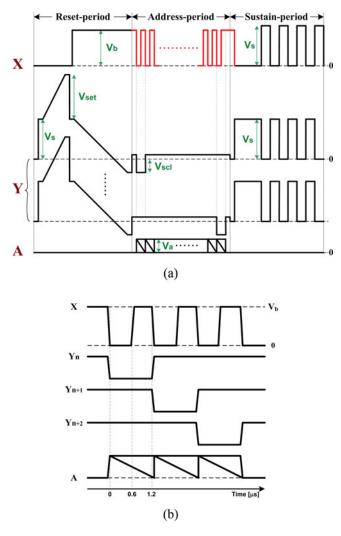

Figure 3(a) shows the proposed driving waveform with additional pulses applied to the X electrode during an address period, and Figure 3(b) shows the enlarged voltage diagram to explain its pulse applying time. To shorten the address discharge delay time by using the wall charges on the X electrodes, as well as the Y and A electrodes, the additional

Table 1. Voltage levels used for conventional and proposed driving waveforms of Figures 1 and 3

| V <sub>set</sub> | $V_s$ | V <sub>b</sub> | V <sub>scl</sub> | Va |

|------------------|-------|----------------|------------------|----|

| 175              | 175   | 150            | -50              | 50 |

Figure 2. Simulation result of wall charge distributions (a) before and (b) after production of address discharge.

pulses were applied to the X electrode during an address period as shown in Figure 3(b) when application of the scan and address pulses started up. The negative going pulse was applied to the X electrode during an address period because the negative charges were accumulated before the production of an address discharge. However, after the production of the address discharge, the applied pulses on the X electrode was maintained with a half time of the address pulse width and returned the original voltage level, because the negative charges were again accumulated on the X electrode for the first sustain discharge. Only if the negative charges should be easily produced at the applying time of the first square sustain pulse to the Y electrode [10]. When the pulse of the next scan line on the Y electrode was adopted, once again the additional pulse on the X electrode was applied for a half time of the address pulse width and return to original voltage level.

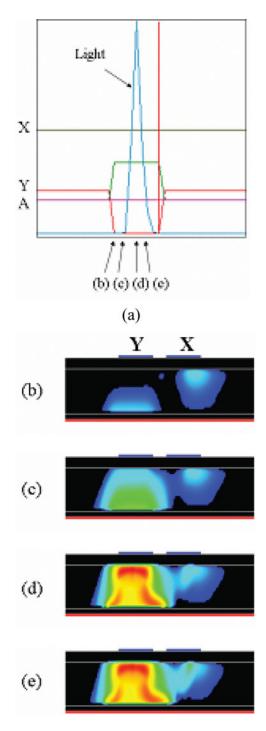

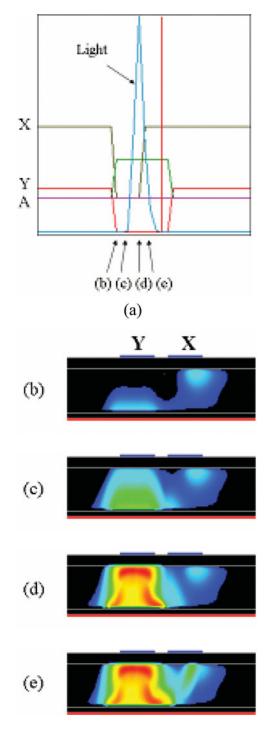

Figure 4(a) shows the simulation waveform in the case of the conventional driving waveform when the scan and address pulses were applied during an address period, and

**Figure 3.** (a) Proposed driving waveform applying pulses on X electrode and (b) enlarged driving waveform during address period.

Figures from 4(b) to 4(e) indicated the simulation results of the Xe  $({}^{3}P_{2})$  energy state for the pulse applying time in Figure 4(a) [8, 9]. Conventionally, the cell of an AC PDP was filled with He-Ne-Xe gas mixture. Among them, as the vacuum ultraviolet (147 nm) emitted by the Xe gas excited the phosphor and produced the visible light, its emission characteristics were important to determine the luminance and luminous efficiency. The Xe  $({}^{3}P_{2})$  energy state significantly affected the transition of the excited atoms and those simulation results were shown in Figures from 4(b) to 4(e). Figure 4(b) shows the energy state at the beginning time of the discharge production after applying the scan and address pulses. The full-scale plasma discharge was found from Figure 4(c) to 4(d) and the address discharge was maintained for some period till the time of Figure 4(e).

Figure 5(a) shows the simulation waveform in the case of the proposed driving waveform when the scan and address pulses were applied during an address period, and Figures

**Figure 4.** Shape of driving waveform used in simulation (a) and changes in Xe  $({}^{3}P_{2})$  energy state in cell from (b) to (e) when applying conventional driving waveform.

**Figure 5.** Shape of driving waveform used in simulation (a) and changes in Xe  $({}^{3}P_{2})$  energy state in cell from (b) to (e) when applying proposed driving waveform.

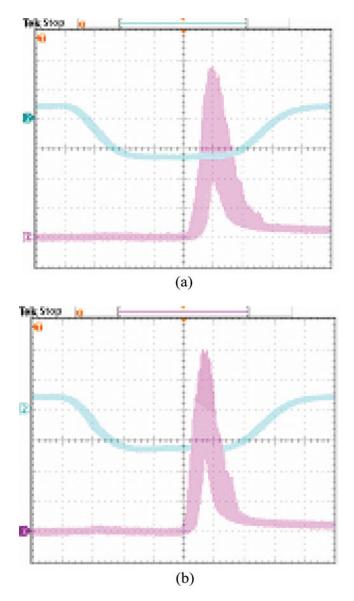

Figure 6. Address discharge light waveform in case of (a) conventional and (b) proposed driving waveform.

from 5(b) to 5(e) indicated the simulation results of the Xe  $({}^{3}P_{2})$  energy state for the pulse applying time in Figure 5(a). Comparing with the simulation result in the conventional driving waveform, it was found that the Xe  $({}^{3}P_{2})$  energy state of the proposed driving waveform in Figure 5(b) was stronger than that of Figure 4 and the plasma discharge was fast produced after applying the scan and address pulses. In addition, the intensity of the energy state in the proposed driving method was also higher than that of the conventional driving method as shown in the simulation result of Figure 5(d) and 5(e).

The optimum driving condition of the proposed driving waveform could be derived from the investigation in the height and the applying time of the pulses on the X electrode during an address period. Figure 6 shows the measured address light waveforms in the case of the conventional driving waveform without applying additional pulse (a) and the proposed driving waveform with additional pulse (b) on the X electrode when the scan and address pulse were applied. Adopting the proposed driving waveform, the start and end time of the address discharge were shown a tendency to produce fast and the discharge time lag could be reduced about 200 ns. Supposing the PDP with HD degree has 768 vertical lines and the number of subfields was 10, the total address time could be shortened about 1.536 ms by the multiplication of 768 lines, 10 subfields, and 200 ns.

## 4. Conclusion

The density and distribution of the wall charge accumulated on three electrodes was investigated after a reset period in AC PDP and the additional pulse on the X electrode was applied in the time of the addressing operation toward the negative direction for improvement of the address discharge by utilizing of the wall charge on overall electrodes. The additional pulse on the X electrode was applied when scan and address pulses were applied, and return to the original voltage level in the middle of the address pulse width. After that, when the next scan and address pulses were applied, the additional pulse was again applied to the X electrode. As a result, comparing the simulation results when the scan pulse was operated in the proposed driving waveform to that in conventional driving waveform, it was found that the plasma discharge was fast produced and the address discharge time could be shortened about 200 ns based on the optimum condition as a result of adopting the proposed driving waveform.

## Funding

This work was supported by a Research Grant of Pukyong National University (2015 year).

#### References

- Saito, A., Maeda, T., Tone, M., Shiga, T., Mikoshiba, S., & Oversluizen, G. (2004). SID '04, 210.

- [2] Park, C. -H., Lee, S. -H., Kim, D. -H., Lee, W. -G., & Heo, J. -E. (2001). *IEEE Trans. Electron Devices*, 50, 2260.

- [3] Cho, B. -G. & Tae, H. -S. (2008). J. of the Society for Information Display, 16, 47.

- [4] Cho, B. -G. (2012). J. of Korean Society for Imaging Science & Technology, 18, 23.

- [5] Kim, J. S., Yang, J. H., Kim, T. J., & Whang, K. W. (2003). *IEEE Trans. Plasma Science*, 31, 1083.

- [6] Shin, B. J., Park, H. D., & Tae, H. -S. (2012). IEICE Trans. Electron, E95-C(5), 958.

- [7] Song, S. -B., Park, P. -Y., Lee, H. -Y., Seo, J. H., & Kang, K. D. (2003). Surface & Coatings Technology, 171, 140.

- [8] Song, S. -B., & Yoon, N. S. (2003). Surface & Coatings Technology, 171, 183–186.

- [9] Kim, J. K., Yang, J. H., Chung, W. J., & Whang, K. W. (2001). *IEEE Trans. Electron Devices*, 48, 1556.

- [10] Cho, B. -G., Tae, H. -S., & Chien, S. -I. (2003), IEEE Trans. Electron Devices, 50, 1758.